# HIGHLY EFFICIENT PMOS BIASEDSENSEAMPLIFER DESIGN

Dr Venkata Subbaiah , Dr Venkata Subbaiah , Dr Venkata Subbaiah , Professor

Department of ECE,

Viswam Engineering College (VISM) Madanapalle-517325 Chittoor District, Andhra Pradesh, India

#### Abstract:

Sense amplifiers plays a significant roleintermsofitsrecital, functionality and reliability of the memory circuits. In this papertwonewcircuitshavebeenproposed. The proposed circuit is PMOS biased sense amplifier, which provides very high output impedance and has reduced sense delay and power dissipation. Assuch, the proposed circuit performs the identical operations as that of conventional circuits but with the reduced the sense delay and power consumption The growing gap between the processor and embedded memory speed is a major setbackin the overall performance of electronic systems. Since the sense amplifier (SA) forms integralpartofthereadcircuitryinbothvolatilememories, such as SRAM, and nonvolatilememories(NVMs), suchasFLASH, its performance has a significant effect on the overall performance of memory. Access time, offset, power and area are the four important performance metrics of SA. The memory accesstime and input-offset of SA greatly affect thespeedoftheentirememoryandthereforetopatch up the gap between processor and memoryspeed, the SA is required to be fast and efficient. As one SA is employed for each bitline in thememory array, it is required to be compact insize and should have low consumption.Furthermorescalingintechnologymakesitdifficulttocontrolthefabricationprocessleadingtovari ationinprocessparameterscausing unpredictability in the performance of SAs. Therefore, it is very important to keep thisaspect in mind while designing and estimatingtheperformance metricsoftheSA This thesis includes the study of various conventional SA designs in detail so as to have

abetterunderstandingofabasicSA and its operation and thus helping in understanding what problems are faced by d esigners in implementing the SA designs and how these problems can

betackled.InadditiontotheconventionalSAanalysis, new sense amplifier designs have

beenproposed for both currents ensing in FLASH memory and voltage sensing in SRAM. Keeping the variation in process parameters due to scaling inmind, these proposed designs have been optimized in terms of access time, offset, power and area.

# Keywords: Sense Amplifier, High Performance, PMOSBiased

# INTRODUCTION

In any digital logic design memories

arethemostimportantblocksinDSP,microprocessors,microcontrollers,andcomputers. Audio players, digital cameras storesthe data in the form of images, audio,

video, speechinaflashmemory should have less power with the display of memory capacity performance on high side on a single chip. Low sensing delay and increased high ercapacities are required for improved quality of stored data. In order to accomplish the towering rate of staging, sense amplifiers are customarily applied to amplify the very small voltage difference on the bit lines at congruous sense timings. If these new sense timings is the sense of the

amplifiers enable signal is asserted early, the SA cannot amplify them inuscule voltage difference accurately. Theover head of access time and power consumption is incremented

if the SAE is asserted tardy. Consequently, the optimum timing for SAE is critical for a high-speed and lowpower SRAM. The memory cellneed to have a mechanism in order to store datapermanently and alter its contents electrically in a non-destructive way. The solution is to alter the threshold voltage of the all so that different threshold values may represent different states of the memory. The two basic states of a flash memory cell are called erased and programmed states. An erased cellissignified by alow threshold value whereas a high threshold

valuesignifiesaprogrammedcell.Equation1.1expresses the relation between the threshold voltage of MOS with the charge stored on the floating gate.

Where K denotes a constant which depends on gate and substrate material, channel

dopingandoxidethickness.Coxdenotesthegate oxide thickness and Q is the charge trappedinto the oxide layer. From the equation it is clearthat the parameter which can be kept in

controltoalterthresholdofthedeviceisQwhichdenotes the charge trapped in the oxide layer. There are charge injection techniques availabletomovechargesinandoutoftheoxide. Anormal MOS device cannot be

used to retain the charges into its oxide thus the device has been modified. A floating gate (FG) device is used for this purpose. FG transistors have the capability to retain charge in the infloating gate for an extended period even after the power supply is turned off.

DuringtheWrite/Programoperation, the control gate and drain are biased at high voltage of 12V for the gate and 5 V for the drain(thevoltagesusedforbiasingareusedasconventionandmayvaryfordifferentmanufacturers), but the source is kept grounded.Underthesecircumstances, averystrongelectric field develops which lets the electronspass from the channel the floating Theseelectrons to gate. overcomethepotentialbarrierposedby the oxide layer and this mechanism is calledHotElectronsInjection. Due to the presence of a high voltage on the drain node, the electrons flowing from thesourcetothedraingainenergyduetotheorthogonal electric Due field. to the presence of high electric fields, electron energy starts to increase and thus electrons are heated, some electrons gain energy high enough to overcome the barrier between the oxide layer and the silicon conduction band. These hotelectrons need to overcome the silicon conduction band and the second secoethebarrierintherightdirection so as to be collected inside the floatinggate. The electrons trapped inside the floatinggate causing the VTH of the flash memory cellto rise. Thus, when a Read operation occurs, switched thecell appears to be in the off state or islogicprogrammed'0', sinceitisunabletoconductcurrentduetoitshighVTH. Thus writing data in a memory cell brings the cellfrom an erased state, which is typically called alogicstate'1', to alogic state'0' or programmed state. The time required for this processisty pically in the range of m

icroseconds. DMA for the purpose of connecting the cell terminals directly to the test mode is used externalInput/outputpads.Thishelpsincharacterization of the memory, the matrix andthe reference cells in particular. It is a difficulttasktofiltertheinterferenceofthememoryarray. Many incorrect outputs can be obtained tothe faults in circuitry if any. For example, if thevoltages are applied in the wrong way or if there is a presence of any voltage spikes or glitches. The possibility of analyzing each and every cellisthereforeavaluableopportunity. Even a single cell can be analyzed with the help of DMA thus proving to be a major test mode. TheDMA test mode setup is shown in Fig. 7. It can be observed from Fig. 7. that in DMA the senseamplifier and the output latch are bypassed suchthatthedrainnodeofthecellisdirectlyconnectedtotheexternalI/Opadwhichisfurtherconnectedtotheextern alsupply. The supply voltage of this external supply is equal to that on the drain in case of a read operation. Also, the gate voltage supplied to selected cellsin DMA mode is supplied through an externalpin. Thissetupenablesthemanufacturertomeasure cell current. transconductance and VTHofcellsundervaryingcondition.

OperatinginDMAmodesoastomeasurethecellcurrentatdifferentbiasvoltagesis a tedious job. Therefore to increase the speedofthisprocedure.FastDMAorFDMAwasintroduced. FDMA mode is similar to the readmode but in **FDMA** mode constant а reference current is maintained and the cell current is compared with it with the help of as ense amplifier. Therefore, the thermal product of the term of tcecurrentcouldbegeneratedinternally or could begenerated externally with the help of the DMA pin. Thegate voltage could be controlled by an externalI/O pad similar to DMA mode. By varying thiscurrent voltage the cell characteristicsare plot. FDMA has an advantage and gate over DMAbeingfasterduetothereadoperation.

ISSN NO: 9726-001X Volume 11 Issue 03 July 2023

#### i.LITERATURESURVEY

It is organizedintofivesections.discusses about few conventional SAdesigns and includes their detailed study. Firstlyintroduces a high speed low offset cross coupled latch type currents enseamplifier for NVM applicationsFlash and the memory in particular. The design and its working has been explained in detail, the design has been simulated an analyzed by inc orporatingVTHvariationsandtheoutputshavebeenpresented.Section4discusses about the low offset high speed crosscoupled latch type SA for SRAMapplications, in which offset and sensing delay lowing havebeen achieved using body biasing techniques. Inthis section, the design has been explained indetail, it has been

simulated and analyzed by incorporating MCVTH variations of 10 mV in all the devices. The outputs for this sense amplifier design for SRAM have been presented.

#### ii.EXISTINGSYSTEM

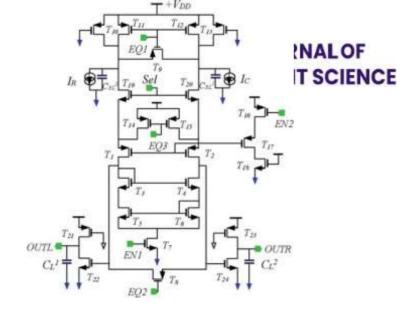

Comparison of different current modes ense amplifiers is presented. In those circuits, we considered PMOS

biased senseamplifiercircuitsasareferencescircuitforproposed method by,making some modificationsin it. In this circuit, there exists two differentialamplifier circuits with current mirrors which ithastobe modified in the proposed circuit

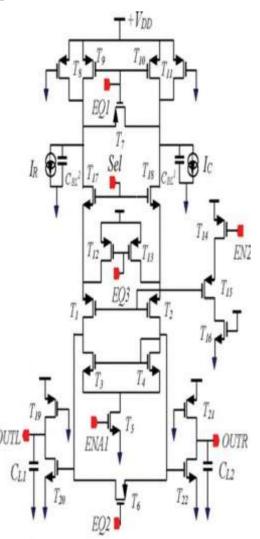

#### iii.PROPOSEDSYSTEM

Afastaccesstimeandlowpowerdissipation are achieved with newly developed circuits of sense amplifier for low voltage supply. In the proposed circuit Here minimizing the mirrortransistor so we can have low power dissipation with high performance and less sense delay.

Fig.1 Existing Sense Amplifier circuit

Fig 2: Proposed Sense Amplifier circuit

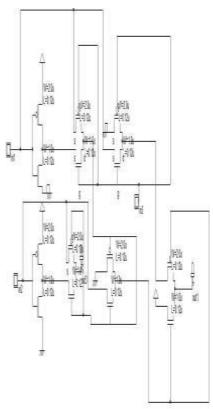

# CIRCUIT DIAGRAM

# Fig 3:PMOSSenseAmplifier 2.WORKINGPRINCIPLE

It has three inputs and two outputs withfive stages. It has Inversion amplifier means itinverse theinputandperformthecircuitandfinaloutputisgivenasinverseoutputforavoidingofconfusion.Stageshelpfor gettinghigh performance with low power dissipation.ItisthecombinationofPMOSandNMOStransistorswhichperformsPMOSasLeadingandNMOSas Lagging.

The circuit consists of 7CMOS transistors which is the combination of PMOS and NMOS. When we provide inputs we get different type of outputs (don't care condition) according to input sprovided. When inputs are

Low, LEDisinOFFstate. When inputs are High, LEDisinON state.

#### **3.SOFTWARE**

DSCHMicrowindisbasicallydigitalschematiccircuitdesigningsoftware. Thisismicrowind simulation software which allows theusers to simulate and design integrated circuit atphysical description level. This is user friendlycircuit simulation software and it supported

byhugesymbollibraries.Microwindunifiesschematic entry, pattern based simulator, SPICEextractionofschematic,Verilogextractor,layoutcompilation,onlayoutmixed-signalcircuit simulation. Microwind software helps todesign various types of logic gates: AND, OR,NOR, NAND, XOR and many advanced designincludedwithhalfadder, fulladder etc.

DSCH The program logic is a editor and simulator. DSCH is used to validate the architecture of the logic circuit before the microelectronics descent the second ssignisstarted.DSCHprovidesauserfriendlyenvironmentforhierarchicallogicdesign, and fast simulati onwith delay analysis which allows the design andvalidation of complex logic structures. **DSCHalso** features the symbols, models and assemblysupportfor8051andPIC16F84controllers.Designerscancreatelogiccircuitsforinterfacing with these controllers and verify software programs using DSCH.

In the first part of this article we willdiscuss thebasic logiccircuit.Inthenext partwewillmovetoadvanceddesign.Let'sconsider 2-input AND gate. Though most of youknowANDgateoperationbutthisarticleistotally introductory level discussion.there is noinput signal so that the output is zero. A HIGHoutput results only if all the inputs to the ANDgate are HIGH If none or not, all inputs to theAND gate are HIGH, a LOW output result.Thefunctioncanbeextendedtoanynumberofinputs.

User-friendly environment for rapid design of logic circuits.

Supportshierarchicallogicdesign.

Addedatoolonfaultanalysisatthegatelevelofdigital.Faults:Stuck-at-1,stuck-at-

0.Thetechniqueallows

injectionofsinglestuck-atfaultatthenodesofthecircuit.

Improved interface between DSCH and Win spice.

with

Handlesboth conventional pattern-basedlogicsimulationandintuitiveonscreenmousedrivensimulation.

Built-inextractorwhichgeneratesaSPICEnetlistfromtheschematicdiagram(Compatible PSPICETMandWinSpiceTM).

GeneratesaVERILOG description of the schematic for layout conversion.

4. ADVANTAGES, DISADVANTAGES& APPLICATIONS

Thisproposedsenseamplifierwhichisimplemented in PMOS process can work atvoltageas lowas 1V. Astheproposed

SAworksat3.3V,thisdesignhas14% and 63% powerdelayproductImprovementovertheadvancedcurrentlatch SAandconventionalsenseamplifier, respectively. Areaisreduced by minimizing of transistors. Sense delayis also reduced Disadvantages: Due process to variations, current mismatchintheevaluationbranchesofthesenseamplifiercircuit, resulting in operational failures. Size of this sens eamplifierarchitectureislarge. The worst power consumption is observed in this type of sense amplifier. APPLICATION Memoryunits. Microprocessors. Microcontrollers. Computers.

# **5.RESULT**

# Fig.4: PMOSsenseAmpliferResult.

Fig.5: Sensing delay vs Different Voltage. 6..CONCLUSION&FUTURESCOPE

Themainaimofthisprojectistoprovidelowpowerdissipationwithhighperformance and less sense delay in memoryunits.

The proposed SA for NVM shows that capacitive coupling with the SA in order to couple the load results in lower power dissipation due to lowering of the standard stanhecouplingeffectatnodes, also the proposed SA senses output fasteratalower voltage offset. The proposed SA for that whenbody biasing used SRAM cell shows is in order to strengthen the positive feed back in the cross coupled SA topology, the SA gives faster results due to lowering of threshold volta in the coupled SA topology and the set of tgesof pulldowns FutureScope:

It has been established that SAs form anintegralpartofanymemoryandthusany

improvement in the speed, yield and offset of the SA will contribute to significantimprovementintheperformanceofmemorycircuitsandsuchimprovementswillhelpbridgeu pthegapbetweenprocessorspeedandmemory. In the future more such topologies could be explored and the current topologiescould be analysed for layout work and chip area.Delay be further can reduced by improving the circuitdesign. Affectof process variations corner and variations on theperformance of the proposed sense amplifiers are not included. So effects of these variations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits and accurate simulations are removed by properdesign of circuits aremoved by properdesign of circuits are removed by prop lations. Yieldmeasurementscan bedone.

#### **7.REFERENCES**

R. Bez, E. Camerlenghi, A. Modelli and A.Visconti, "IntroductiontoFlashMemory,"inProceedingsoftheIEEE,2003.

R. Bez, E. Camerlenghi, A. Modelli and A.Visconti, "IntroductiontoFlashMemory," in Proceedings of the IEEE, 2003.

A. Pavlov and M. Sachedev, CMOS SRAMCircuitDesignandparametrictestinnano-scaledtechnologies,Berlin:Springer-verlag,2008.

A. A. M. "Design and analysis of a high-speedsenseamplifierforsingle-transistornonvolatile memory cells," in IEEE ProceedingsG-Circuits, Devices and Systems, 1993.

A. A. M. "Design and analysis of a high-speedsenseamplifierforsingle-transistornonvolatile memory cells," in IEEE ProceedingsG-Circuits, Devices and Systems, 1993.

D.J.RennieandM.Sachdev, "SRAMSense Amplifier". USA Patent US 8536898 B2, 17 september 2013.

[7].B. Azeez, T. Xinghai and J. Meindl, "TheImpactofIntrinsicDeviceFluctuationsonCMOS SRAM Cell Stability," IEEE Journal ofSolid-State Circuits, vol. 36, no. 4, pp. 658-665,2001